## (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ЕВРАЗИЙСКОМУ ПАТЕНТУ

(45) Дата публикации и выдачи патента

(51) Int. Cl. *H04L 12/66* (2006.01)

2021.12.17

**(21)** Номер заявки

201892273

(22) Дата подачи заявки

2018.11.07

## (54) УСТРОЙСТВО ЦИФРОВОГО СОПРЯЖЕНИЯ ІР

(43) 2020.05.31

(96)2018000132 (RU) 2018.11.07

**(71)(73)** Заявитель и патентовладелец:

ОТКРЫТОЕ АКЦИОНЕРНОЕ ОБЩЕСТВО "МЕЖГОСУДАРСТВЕННАЯ КОРПОРАЦИЯ РАЗВИТИЯ" (RU)

**(72)** Изобретатель:

Старченков Владимир Александрович (RU)

(74) Представитель:

Левчук Д.В., Ловцов С.В., Вилесов А.С., Коптева Т.В., Ясинский С.Я. (RU)

"Выбор НИКОНОВА A.O. структурного решения для функционального блока многофункционального конвертера интерфейсов", Электронный научно-практический "Современные научные исследования инновации", №8, 2016, Найдено в Интернет <URL: http://web.snauka.ru/issues/2016/08/70253>, рис. 1, 3

RU-U1-50693 RU-U1-80039 RU-U1-179300 RU-C1-2479904

Изобретение относится к технике электросвязи, а именно предназначено для передачи цифровых низкоскоростных каналов (С1-ФЛ-БИ, RS-232 и ОЦК - основной цифровой канал) по сетям пакетной передачи данных с ІР-протоколом. Изобретение может использоваться для соединения фрагментов сети с временным уплотнением каналов по проводным и беспроводным пакетным сетям связи. Изобретение решает задачу расширения функциональных возможностей устройства. Технический результат, на достижение которого направлено изобретение, заключается в обеспечении возможности подключения оконечного оборудования по стыкам ОЦК, С1-ФЛ-БИ и RS-485. УЦС IP включает приемопередатчик С1-ФЛ-БИ 1, приемопередатчик ОЦК 2, входамивыходами соединенные с ПЛИС 3, которая по шине данных 4 и по шине адреса 5 связана с оперативным запоминающим устройством 6 и с микропроцессором 7. Микропроцессор 7 входамивыходами соединен с приемопередатчиком RS-232/RS-4858 и с приемопередатчиком Ethernet 9.

Изобретение относится к технике электросвязи, а именно предназначено для передачи цифровых низкоскоростных каналов (С1-ФЛ-БИ, RS-232 и ОЦК - основной цифровой канал) по сетям пакетной передачи данных с IP-протоколом. Изобретение может использоваться для соединения фрагментов сети с временным уплотнением каналов по проводным и беспроводным пакетным сетям связи.

Известен конвертер Ethernet-C1-И, предназначенный для приема и передачи сигналов интерфейса Ethernet по линиям интерфейса C1-И. (http://www.supertel.ru/conv-eth-sl-i). В состав конвертера включены разъемы C1-И, преобразователь МП-C1-И, коммутатор на основе MAC-адресов, генератор, блок питания и разъемы LAN (Ethernet). Недостатком аналога является отсутствие возможности передачи сигналов ОЦК по IP-сети, отсутствие возможности подключения оборудования по стыкам RS-232 и RS-485.

Наиболее близким техническим решением, принятым в качестве прототипа, является блок многофункционального конвертера интерфейсов на основе программируемой логической интегральной схемы (далее - ПЛИС) и микроконтроллера (Никонова А.О. Выбор структурного решения для функционального блока многофункционального конвертера интерфейсов // Современные научные исследования и инновации. 2016. № 8 [Электронный ресурс]. URL: http://web.snauka.ru/issues/2016/08/70253, см. рис. 3). В состав конвертера входят последовательно соединенные двухсторонней связью блок RS-232, ПЛИС, микроконтроллер, блок Ethernet. С ПЛИС подаются управляющие сигналы на блок ключей. Микроконтроллер выполняет прием/передачу данных по Ethernet. ПЛИС осуществляет прием/передачу и обработку данных каналов RS-232, организует доступ микроконтроллера к полученным данным. Недостатком прототипа является отсутствие возможности подключения оконечного оборудования по стыкам ОЦК, С1-ФЛ-БИ и RS-485.

Изобретение решает задачу расширения функциональных возможностей устройства. Технический результат, на достижение которого направлено изобретение, заключается в обеспечении возможности подключения оконечного оборудования по стыкам ОЦК, С1-ФЛ-БИ и RS-485.

Указанный технический результат достигается тем, что в устройство цифрового сопряжения IP (далее - УЦС IP), включающее ПЛИС, приемопередатчик RS-232 и приемопередатчик Ethernet, введены приемопередатчик C1-ФЛ-БИ, приемопередатчик основного цифрового канала, микропроцессор, соединенный входами-выходами по шине адреса и по шине данных с оперативным запоминающим устройством и с программируемой логической интегральной схемой. При этом приемопередатчик RS-232 выполнен в виде совмещенного приемопередатчика RS-232/RS-485, соединен входом-выходом с микропроцессором, который, в свою очередь, соединен входом-выходом с приемопередатчиком Ethernet. Приемопередатчик C1-ФЛ-БИ и приемопередатчик основного цифрового канала соединены входами-выходами с ПЛИС.

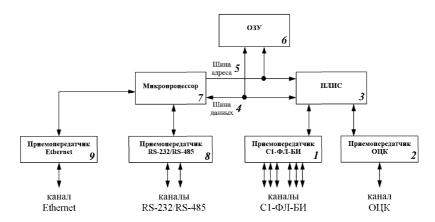

Изобретение поясняется чертежом, на котором приведена структурная схема УЦС ІР.

УЦС IP включает приемопередатчик С1-ФЛ-БИ 1, приемопередатчик ОЦК 2, входом-выходом соединенный с ПЛИС 3, которая входами-выходами по шине данных 4 и по шине адреса 5 соединена с оперативным запоминающим устройством 6 и с микропроцессором 7. Микропроцессор 7 входами-выходами соединен с приемопередатчиком RS-232/RS-4858 и с приемопередатчиком Ethernet 9.

УЦС IP работает следующим образом.

Сигнал ОЦК поступает на вход приемопередатчика ОЦК 2, в котором сравниваются и выделяются сигналы отдельно для положительных и отрицательных уровней. Далее выделенные цифровые сигналы поступают в ПЛИС 3. ПЛИС 3 осуществляет тактовую и октетную синхронизации потока и декодирование информации.

Сигнал С1-ФЛ-БИ поступает на вход приемопередатчика С1-ФЛ-БИ 1, который компарирует входное напряжение и выдает цифровой сигнал. Полученный сигнал поступает в ПЛИС 3. ПЛИС 3 осуществляет тактовую синхронизацию потока и декодирование информации.

Дальнейшая обработка осуществляется аналогично для потоков ОЦК и С1-ФЛ-БИ. Принимаемые информационные биты сигнала поступают в сдвиговый регистр, реализованный в ПЛИС 3. При заполнении регистра данные переписываются в буфер, реализованный в ПЛИС 3 и организованный по принципу очереди (FIFO, "первый пришел - первый ушел"). При заполнении очереди выше определенного уровня, который задается программно, в зависимости от скорости канала, генерируется запрос на прерывание, который передается в микропроцессор 7. Микропроцессор 7 обрабатывает запрос, считывает данные, формирует пакеты в соответствии с протоколом UDP/IP и передает пакеты на приемопередатчик Ethernet 9.

При приеме пакетов UDP/IP они поступают в микропроцессор 7 через приемопередатчик Ethernet 9. При этом возможно изменение порядка поступления пакетов по сравнению с исходным. Поэтому каждый пакет снабжен номером, который циклически увеличивается на единицу для каждого следующего пакета. При приеме в микропроцессоре 7 происходит сравнение номера приходящего пакета с ожидаемым номером. Если номер оказывается меньше ожидаемого, то пакет был продублирован сетью передачи и он отбрасывается. Если номер пакета больше ожидаемого, то пакет запоминается. Если номер равен ожидаемому, то пакет записывается в ПЛИС 3 (возможно, с другими ранее сохраненными пакетами). Таким образом восстанавливается исходная последовательность переданных пакетов.

При передаче данных по сети с коммутацией пакетов появляется переменная временная задержка

(джиттер). Для предотвращения разрывов выходных потоков ОЦК и С1-ФЛ-БИ в УЦС ІР реализуется буфер передачи. Поступающие пакеты данных после восстановления последовательности записываются в буфер, реализованный в ПЛИС. При этом поддерживается заполнение буфера на заданном уровне, для чего регулируется в небольших пределах выходная скорость передачи канала.

Настройка и конфигурирование УЦС IP осуществляется с персонального компьютера, подключенного по стыку RS-232 (RS-485) через приемопередатчик RS-232/RS-4858 или Ethernet через приемопередатчик Ethernet 9.

ОЗУ 6 служит для хранения данных и программы микропроцессора 7.

УЦС IP обеспечивает передачу цифровых потоков при работе в сетях с большим джиттером задержки пакетов (например, сети сотовых операторов связи). Для увеличения надёжности передачи потоков ОЦК и С1-ФЛ-БИ обеспечивается многократная передача IP-пакетов (реализовано в микропроцессоре). На приёмной стороне осуществляется восстановление исходной последовательности пакетов. Например, можно передавать непрерывные потоки по нескольким каналам сотовой связи.

## ФОРМУЛА ИЗОБРЕТЕНИЯ

Устройство цифрового сопряжения IP, состоящее из программируемой логической интегральной схемы, предназначенной для тактовой и октетной синхронизации потока и декодирования информации, и приемопередатчика RS-232 и приемопередатчика Ethernet, предназначенных для передачи IP-пакетов в сеть,

отличающееся тем, что дополнительно включает приемопередатчик С1-ФЛ-БИ, приемопередатчик основного цифрового канала, выполненный с возможностью сравнения и выделения сигналов отдельно для положительных и отрицательных уровней, связанный двусторонне с программируемой логической интегральной схемой для передачи выделенных сигналов, причем программируемая логическая интегральная схема снабжена сдвиговым регистром для записи принимаемых сигналов и буфером для переписи сигналов при заполнении регистра, микропроцессор, выполненный с возможностью обработки запроса на прерывание от программируемой логической интегральной схемы по шине адреса и по шине данных с оперативного запоминающего устройства, при этом приемопередатчик RS-232 выполнен в виде совмещенного приемопередатчика RS-232/RS-485 с возможностью подключения персонального компьютера и двусторонне связан с микропроцессором для настройки и конфигурирования устройства цифрового сопряжения IP, с которым двусторонне связан приемопередатчик Ethernet для передачи IP-пакетов.

1

Евразийская патентная организация, ЕАПВ

Россия, 109012, Москва, Малый Черкасский пер., 2