# (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ЕВРАЗИЙСКОМУ ПАТЕНТУ

(45) Дата публикации и выдачи патента

(51) Int. Cl. *G06F 13/372* (2006.01)

2020.08.06

(21) Номер заявки

201990877

(22) Дата подачи заявки

2017.10.31

СТРУКТУРА ПО СЕРТИФИЦИРУЕМОЙ СИСТЕМЫ УПРАВЛЕНИЯ С ПОСТОЯННЫМИ ПАРАМЕТРАМИ ДЛЯ ПРИЛОЖЕНИЙ ЖЕСТКОГО РЕАЛЬНОГО ВРЕМЕНИ, КРИТИЧЕСКИХ С ТОЧКИ ЗРЕНИЯ БЕЗОПАСНОСТИ, В СИСТЕМАХ БОРТОВОГО РАДИОЭЛЕКТРОННОГО ОБОРУДОВАНИЯ С ИСПОЛЬЗОВАНИЕМ **МНОГОЯДЕРНЫХ ПРОЦЕССОРОВ**

(31) 102016000109768 (**56**) US-B1-8943287

US-A1-2012084525 US-A1-2014379953

(32)2016.10.31

(33)IT

(43) 2019.08.30

(86) PCT/IB2017/056769

(87) WO 2018/078610 2018.05.03

(71)(73) Заявитель и патентовладелец:

**ЛЕОНАРДО С.П.А. (ІТ)**

(72) Изобретатель:

Соцци Марко, Траверсон Массимо

(IT)

(74) Представитель:

Абраменко О.И. (RU)

Система РЭО (1), состоящая из центрального процессорного устройства (2) для реализации одного (57) или более приложений жесткого реального времени, критических с точки зрения безопасности, центральное процессорное устройство (2) включает в себя многоядерный процессор (3) с множеством ядер (4), программное обеспечение системы РЭО, выполняемое многоядерным процессором (3), память (6), общую шину (8), по которой многоядерный процессор (3) может получить доступ к памяти (6); система РЭО (1), отличающаяся тем, что программное обеспечение системы РЭО спроектировано таким образом, чтобы оно предписывало во время осуществления ядрам (4) многоядерного процессора (3) обращаться за доступом к памяти (6) по общей шине (8) посредством распределения пропускной способности шины в соответствии с выделенными распределениями пропускной способности шины.

#### Притязание на приоритет

По настоящей заявке испрашивается приоритет по заявке на выдачу патента Италии № 102016000109768 с датой подачи 31.10.2016 г., описание сущности которой включено в настоящую заявку посредством ссылки.

#### Область техники

Изобретение относится к системам бортового радиоэлектронного оборудования, а именно к электронным системам, используемым в аэронавтике и космонавтике на воздушных судах, искусственных спутниках и космических кораблях, и в частности, к структуре программного обеспечения сертифицируемой системы управления с постоянными параметрами для приложений жесткого реального времени, критических с точки зрения безопасности, в системах бортового радиоэлектронного оборудования с использованием многоядерных процессоров.

# Уровень техники

Как известно, системы бортового радиоэлектронного оборудования (как с точки зрения авиации, так и электроники) составляют все возрастающую часть себестоимости воздушного судна и отвечают за различные приложения, такие как навигация, система наведения, устойчивость, управление подачей топлива, связь "воздух-земля", развлечение пассажиров, управление полетом и т.д.

Системы бортового радиоэлектронного оборудования стали центральными элементами воздушных судов и должны отвечать широкому спектру требований, таким как надежность при отказах оборудования, детерминизм и работа в режиме реального времени.

В ответ на эти требования производителями воздушных судов были предложены различные архитектуры систем бортового радиоэлектронного оборудования, включая недавнюю архитектуру системы Интегрированной Модульной Авионики (ИМА), которая устанавливается на воздушные суда самой последних моделей, и в которой в отличие от традиционной архитектуры бортового радиоэлектронного оборудования системы бортового радиоэлектронного оборудования обладали своими собственными отдельными ресурсами РЭО (радиоэлектронного оборудования), ресурсы РЭО распределяются между несколькими системами РЭО. Ресурсы РЭО, которые обычно распределяются, представляют собой компьютеры с системами, работающими в режиме реального времени, или локальную сеть с протоколами связи в режиме реального времени.

Новая архитектура системы ИМА способствовала разработке так называемых х-электродистанционных распределенных приложений, а именно приложений РЭО, имеющих отношение к безопасности, таких как пилотирование, торможение, управление полетом, которые зависят от коммуни-кационной сети реального времени для подсоединения различных электронных элементов.

Среди ограничений, которые должны соблюдать системы РЭО, условия реального времени играют первостепенную роль и оказывают непосредственное влияние на конфигурацию архитектуры на уровне воздушного судна и системы, а также на процесс валидации/сертификации. Таким образом, производители воздушных судов должны продемонстрировать соответствие международным нормам, используя средства, которые были приемлемыми для сертификационных органов. Это включает в себя демонстрацию того, что все требования безопасности выполнены, гарантируя функционирование связи, расчет рабочих характеристик в режиме реального времени, а также разработку программного и аппаратного обеспечения в соответствии со строгими принципами разработки.

Параллельно с этим разрабатываются информационные и коммуникационные технологии наряду с технологиями производства процессоров, а также предлагаются новые решения для РЭО.

В частности, в течение последних лет на всех коммерческих доменах, включая РЭО, наблюдается все ускоряющееся исчезновение одноядерных процессоров и системное появление многоядерных процессоров, состоящих из нескольких ядер.

Они обладают высокой интеграцией и надлежащим соотношением между техническими характеристиками и мощностью благодаря распределению ресурсов между ядрами. Поэтому они предлагают многообещающие возможности из-за их высокого уровня вычислительной способности. Предполагается, что надлежащим образом управляемые многоядерные системы будут гарантировать соответствующее повышение вычислительной способности, необходимой для сложных приложений, таких как сложные системы управления полетом, которые требуют короткого времени отклика и огромных расчетов. Стандартные многоядерные процессоры состоят в среднем из 2-8 ядер, установленных на микросхеме, но максимальное количество ядер может составлять 16.

Обычно ядра состоят из одного или двух уровней индивидуальных команд (инструкций), кэша данных и распределяемого (разделяемого) дополнительного уровня, наряду с общей шиной к основной памяти. Подобные архитектуры часто применяют жесткую схему когерентности кэша, которые позволяют выполнять параллельные приложения, спроектированные в соответствии с очень удобной моделью программирования распределенной памяти.

Однако реализация многоядерных процессов в системах РЭО представляет собой сложную задачу. Фактически, работа многоядерных процессоров подразумевает интенсивное распределение ресурсов и некоторых непредсказуемых механизмов управления распределением ресурсов, что усложняет предсказуемость по времени.

Распределение (разделение) ресурсов делает временной анализ критичных в отношении безопасности систем очень сложным, если не неосуществимым. Это происходит из-за трудности учета всех возможных межзадачных конфликтов, в частности, если контроллер когерентности кэша генерирует неявные сообщения.

В частности, задачи, которые необходимо решить проектировщикам критичных в отношении безопасности систем РЭО, включают в себя определение наихудшего времени исполнения (WCET), наихудшего времени связи (времени коммуницирования/взаимодействия) и наихудшего времени доступа к памяти для любой задачи для проверки постоянного выполнения жестких требований к работе в режиме реального времени.

Существует несколько подходов или они были предложены для улучшения ситуации с анализом наихудшего случая.

Первый способ - это проектирование особых прогнозируемых архитектур многоядерных процессоров, в которых гарантируется детерминированный режим критичных в отношении безопасности приложений посредством обеспечения выполнения критичных в отношении безопасности приложений только на одном ядре, в то время как прочие ядра не используются.

Второй способ - это временно-ориентированный подход, в соответствии с которым применяется модель выполнения, где определены правила, которые ограничивают режим критичных в отношении безопасности приложений в пределах соответствующих временных интервалов и снижают количество непредсказуемых режимов.

В дополнение к вышеизложенному авиационные сертифицирующие органы, такие как Федеральная Авиационная Администрация США (ФАА) и Европейское агентство по безопасности полетов (EASA), выражают озабоченность в отношении применения многоядерных процессоров (МЯП) в критичных в отношении безопасности систем РЭО (Уровень гарантии проектирования (DAL) А, В или С) из-за потенциальных недетерминированных архитектур многоядерных процессоров и общей сложности систем, использующих данные процессоры.

По этим причинам использование многоядерных процессоров в системах РЭО, предназначенных для реализации в приложениях РЭО жесткого реального времени, критических с точки зрения безопасности, в настоящее время представляет собой очень сложную задачу для проектировщиков систем РЭО, а прогнозируемость наихудшего случая является одной из наиболее сложных задач в результате того, что минимизация рисков может оказаться очень сложной с различных точек зрения, в особенности в отношении времени и издержек.

В патенте США 2012/0084525 А1 описываются метод и устройство для загрузки и выполнения команд с детерминированными циклами в многоядерной системе РЭО, имеющей шину, время доступа к которой непредсказуемо. Система РЭО включает в себя многоядерный процессор, состоящий как минимум из 2 ядер и контроллера памяти, каждое из ядер обладает своей собственной (индивидуальной) памятью. Совокупность команд загружается и выполняется в течение интервалов выполнения таким образом, чтобы во время первого интервала выполнения первое ядро имело доступ к контроллеру памяти для передачи как минимум одной единицы информации, которая хранится в его собственной памяти, и для получения и сохранения как минимум одной единицы информации, и команды из совокупности команд в его собственной памяти в то время как второе ядро не имеет доступа к контроллеру памяти, и выполняет как минимум одну команду, ранее сохраненную в его собственной памяти, и таким образом, во время второго интервала выполнения роли двух ядер меняются местами.

Вышеуказанные уровни техники принципиально основываются на парадигме ограничения процессорного ядра, в соответствии с которой только одно ядро в многоядерном процессоре допускается к работе, или в парадигме ограничения по времени, в соответствии с которой одновременная работа ядер в многоядерном процессоре предотвращается посредством их работы в соответствии с надлежащими временными интервалами, что приводит к неэффективному использованию вычислительного ресурса.

В патенте США 8943287 В1 описывается многоядерная процессорная система, сконфигурированная для ограничения скорости доступа со стороны памяти. Многоядерная процессорная система включает в себя несколько процессорных ядер, систему памяти и общую шину доступа, которая соединяет ядра и систему памяти. Каждое ядро состоит из центрального процессора, выделенного кэша ядра, функционально подсоединенного к центральному процессору, и ограничителя скорости передачи центрального процессора, функционально подключенного к выделенному кэшу ядра. Система памяти состоит из физической памяти, предпочтительно из памяти с удвоенной скоростью передачи данных (DDR), а точнее из памяти DDR SDRAM (синхронное динамическое ОЗУ с удвоением тактовой частоты шины данных), контроллера памяти, функционально подключенного к физической памяти, и выделенного кэша памяти, подсоединенного к контроллеру памяти. Ограничители скорости передачи центрального процессора сконфигурированы таким образом, чтобы ограничивать скорость, с которой данные оцениваются каждым соответствующим центральным процессором со стороны системы памяти для того, чтобы доступ к памяти каждого центрального процессора мог ограничиваться в соответствии с заданным значением. В результате ограничения скорости многоядерная процессорная система обеспечивает асинхронное функционирование центральных процессоров для обеспечения пропускной способности DDR, которая требу-

ется для выполнения заданных сроков обработки.

### Сущность изобретения

Заявитель признает, что подход, приведенный в патенте США 8943287 В1, который в результате приводит к асинхронному функционированию ядер в многоядерном процессоре, направлен на устранение трудностей современных подходов, рассматриваемых в патенте США 8943287 В1 и возникших в результате относительно большого количества ограничений, налагаемых на работу многоядерных процессорных систем в системах РЭО для обеспечения требований безопасности, в то время как в патенте 8943287 В1 идентифицированы упущения неэффективного или малоэффективного применения многоядерных процессоров в системах РЭО, которые возрастают по мере увеличения количества ядер в центральном процессоре, а при использовании относительно сложной конфигурации, если наблюдаются нежелательные периоды простоя, приводят к необходимости синхронизации ядер в многоядерных процессорах.

Целью данного изобретения является обеспечение структуры ПО системы РЭО, которая позволит использовать вычислительные ресурсы многоядерных процессоров, встроенных в системы РЭО, предназначенных для реализации приложений РЭО жесткого реального времени, критических с точки зрения безопасности, подлежащих усовершенствованию, без негативных последствий для истинного детерминированного режима приложений жесткого реального времени, критических с точки зрения безопасности.

Настоящее изобретение относится к системе РЭО, программному обеспечению системы РЭО, способу определения пропускной способности шины в системе РЭО и способу определения совместного использования пропускной способности шины системы РЭО, как заявлено в прилагаемых пунктах формулы изобретения.

Система РЭО (1) состоит из центрального процессорного устройства (2) для реализации одного или нескольких приложений жесткого реального времени, критических с точки зрения безопасности, центральное процессорное устройство (2) включает в себя многоядерный процессор (3) с множеством ядер (4), память (6), общую шину (8), по которой многоядерный процессор (3) может получить доступ к памяти (6), и программное обеспечение РЭО, выполняемое многоядерным процессором (3), предписывает во время выполнения ядрам (4) многоядерного процессора (3) обращаться за доступом к памяти (6) по общей шине (8) посредством распределения пропускной способности шины в соответствии с выделенным распределением пропускной способности шины;

отличающаяся тем, что программное обеспечение системы РЭО предназначено для того, чтобы при его осуществлении предписывать планирование периодических проверок фактического использования пропускной способности шины ядрами (4) многоядерного процессора (3) в отношении выделенных распределений пропускной способности шины для определения тех ядер (4) в многоядерном процессоре (3), которые в конечном счете выходят за пределы выделенного распределения пропускной способности шины, а также планирование перевода в режим ожидания ядер (4), которые были определены как вышедшие за пределы выделенных распределений пропускной способности шины для компенсации переработки:

а также тем, что программное обеспечение системы РЭО также предназначено для того, чтобы при его осуществлении предписывать планирование проверок фактического использования пропускной способности шины ядрами (4) в многоядерном процессоре (3) относительно выделенных распределений пропускной способности шины синхронно по всем ядрам (4) для получения фактического использования пропускной способности шины ядер (4) в многоядерном процессоре (3) при одновременной проверке. В некоторых вариантах реализации программное обеспечение системы РЭО предназначено для того, чтобы предписывать при его выполнении переводить в режим ожидания ядра (4) в многоядерном процессоре (3), которые были определены как вышедшие за пределы выделенных распределений пропускной способности шины, в течение одного или более временных интервалов между следующими запланированными проверками для компенсации переработки.

В некоторых вариантах реализации ядра (4) многоядерного процессора (3) оборудованы подсоединенными счетчиками производительности (10) для подсчета операций, выполняемых соответствующими ядрами (4); в которой программное обеспечение системы РЭО предназначено для того, чтобы при его выполнении предписывать счетчикам производительности (10) выполнять подсчет количества обращений ядер (4) в многоядерном процессоре (3) к памяти (6) по общей шине (8), что приводит к подсчетам счетчиком производительности (10), которые отражают фактическое использование пропускной способности шины соответствующими ядрами (4) в многоядерном процессоре (3); и в которой программное обеспечение системы РЭО также предназначено для того, чтобы при его осуществлении предписывать и планировать счетчикам производительности (10) периодически выполнять считывание, а также проверять показания подсчетов счетчиков производительности (10) относительно соответствующих выделенных индикативных значений распределений пропускной способности шины, выделенных ядрам (4) в многоядерном процессоре (3) для определения ядер (4), которые в конечном счете вышли на пределы выделенных распределений пропускной способности шины.

В некоторых вариантах реализации программное обеспечение системы РЭО также предназначено

для того, чтобы при его выполнении предписывать первому счетчику производительности (10) выполнять подсчет количества операций записи и считывания строк кэша, второму (10) выполнять подсчет количества операций считывания строки кэша команд, а третьему счетчику производительности (10) и четвертому счетчику производительности (10) выполнять подсчет количества операций заполнения кэша ТLB (буфера ассоциативной трансляции); и в которой программное обеспечение системы РЭО также предназначено для того, чтобы при его выполнении предписывать выполнение расчета количества обращений ядер (4) к памяти (6) по общей шине (8) в виде суммы подсчитанного количества операций записи и считывания строк кэша данных, операций считывания строк кэша команд и операций заполнения кэша ТLB (буфера ассоциативной трансляции).

В некоторых вариантах реализации пропускная способность шины равномерно распределяется среди ядер (4) в многоядерном процессоре (3).

В некоторых вариантах реализации многоядерный процессор (3) предназначен для доступа к периферийным устройствам (9) по общей шине (8), а программное обеспечение системы РЭО спроектировано таким образом, чтобы при его выполнении предписывать только одному основному ядру (4) многоядерного процессора (3) управлять доступом к периферийным устройствам (9) из всех ядер (4) в многоядерном процессоре (3), что приводит к тому, что прямой доступ к периферийным устройствам (9) предоставляется только основным ядром (4) при наличии непрямого доступа со стороны вторичных ядер (4) через основное ядро.

В некоторых вариантах реализации программное обеспечение системы РЭО также предназначено для того, чтобы при его выполнении предписывать обращение основного ядра (4) к периферийным устройствам (9) для считывания с них данных или записи на них данных, предшествовало или следовало за ним соответствующее обращение основного ядра (4) к памяти (6) для записи в память (6) данных, считанных с периферийных устройств (9) или считывания из памяти (6) данных, записанных на периферийных устройствах (9), создавая таким образом связь между обращениями к периферийным устройствам и памяти, что приводит к расчету пропускной способности шины, которая требуется для обращения к периферийным устройствам (9) на основании пропускной способности шины, необходимой для обращения к памяти (6).

В некоторых вариантах реализации программное обеспечение системы РЭО также предназначено для того, чтобы при его осуществлении при предписывании обращения основного ядра (4) к периферийным устройствам (9) назначается весовая функция, которая выше, чем весовая функция, назначенная для обращения основного ядра (4) к памяти (6), что приводит к тому, что пропускная способность шины, необходимая для обращения к периферийным устройствам (9), рассчитывается на основании пропускной способности, необходимой для обращения к памяти (6), а весовые функции назначаются для обращения основного ядра (4) к периферийным устройствам (9) и памяти (6). В некоторых вариантах реализации весовая функция, назначенная для обращения основного ядра (4) к периферийным устройствам (9), зависит от типа периферийного устройства (9), к которому обеспечивается доступ.

Способ категоризации пропускной способности шины в системе РЭО (1) по любому из предшествующих пунктов формулы изобретения при фиксированной рабочей частоте, на которой многоядерный процессор (3) подлежит применению при использовании, способ включает

инициацию работы многоядерного процессора (3) с фиксированной рабочей частотой,

предписание только одному основному ядру из ядер (4) в многоядерном процессоре (3) циклически обращаться к памяти (6) по общей шине (8) для передачи строк кэша фиксированного размера,

определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени и

определение пропускной способности шины на основании количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени и размера строк кэша.

В некоторых вариантах реализации способа ядра (4) в многоядерном процессоре (3) оборудованы соответствующими счетчиками производительности (10) для подсчета операций, выполняемых соответствующими ядрами (4); в котором определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени включает в себя

предписание одному или более счетчикам производительности (10) основного ядра (4) выполнить подсчет обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени.

считывание показаний счетчика(-ов) производительности (10) основного ядра (4), которые участвуют в подсчете количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени, и

определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени на основании показаний, считанных со счетчиков производительности (10).

В некоторых вариантах реализации способ дополнительно включает

предписание прочим ядрам (4) в многоядерном процессоре (3) функционировать в бесконечном замкнутом цикле без доступа к памяти (6) по общей шине (8).

Способ определения распределений пропускной способности шины, подлежащих выделению ядрам (4) в многоядерном процессоре (3) в системе РЭО (1), способ включает в себя

определение характеристик пропускной способности шины по любому из предшествующих пунктов формулы изобретения 10-12 и

распределение пропускной способности шины среди ядер (4) в многоядерном процессоре (3).

Способ определения распределений пропускной способности шины, в котором распределение пропускной способности шины среди ядер (4) в многоядерном процессоре (3) состоит из

равного распределения пропускной способности шины среди ядер (4) в многоядерном процессоре (3).

# Краткое описание чертежей

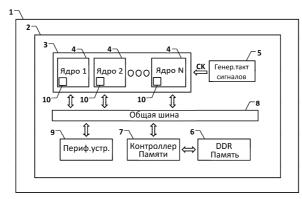

На фиг. 1 схематично изображена блок-схема многоядерного центрального процессора, встроенного в систему жесткого реального времени РЭО, критической с точки зрения безопасности.

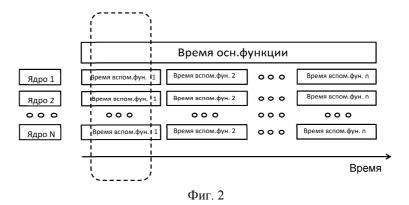

На фиг. 2 схематично показаны максимальные и минимальные временные разделения синхронизации между ядрами многоядерного центрального процессора.

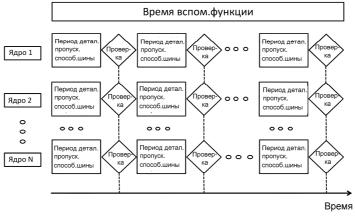

На фиг. 3 схематично показаны периодические проверки, одновременные для всех ядер, при использовании пропускной способности ядрами, относительно распределенного совместного использования пропускной способности шины.

На фиг. 4 показан процесс контроля пропускной способности, который выполняется ядром процессора.

## Детальное описание вариантов осуществления изобретения

Описание изобретения дается с учетом прилагаемых чертежей для возможности его реализации и использования специалистом. Различные модификации описанных способов осуществления изобретения станут сразу же очевидными для опытного специалиста, а общие описанные принципы могут применяться к другим способам осуществления изобретения и применений, не выходя при этом из объема правовой охраны настоящего изобретения, как это определено в прилагаемой формуле изобретения. Поэтому настоящее изобретение не должно ограничиваться только формами описанных и проиллюстрированных способов изобретения, но должно иметь широкую правовую охрану в соответствии с описанными и заявленными способами и отличительными признаками.

На фиг. 1 схематично показана блок-схема системы РЭО 1, состоящая (включающая) из многоядерного центрального процессорного устройства (ЦПУ) 2 для реализации приложений жесткого реального времени, критических с точки зрения безопасности, таких как управление полетом (контроль полета), оптимизация режимов полета, навигация, система наведения, устойчивость, управление подачей топлива (регулирование подачи топлива), связь "воздух-земля" и т.д.

Центральное процессорное устройство 2 надлежащим образом состоит из усовершенствованной архитектуры или архитектуры машины с сокращенным набором команд (Acorn RISC Machine (ARM)) и включает в себя многоядерный процессор 3 с множеством ядер 4, программное обеспечение системы РЭО выполняется многоядерным процессором 3, генератором тактовых сигналов 5, спроектированным для подачи на многоядерный процессор 3 синхронизирующего сигнала СК, памятью 6 с сопряженным (соединенную с) контроллером памяти 7, и общей шиной 8, посредством которой многоядерный процессор 3 может получить доступ как к памяти 6 через сопряженный контроллер памяти 7, так и к встроенным периферийным устройствам 9, а также к внешним устройствам посредством подсоединенных интерфейсов ввода/вывода (не показаны на чертежах).

В общих чертах сертифицируемый истинно детерминированный режим абсолютно всех приложений жесткого реального времени РЭО, критических с точки зрения безопасности, выполняемых многоядерным ЦПУ 2, достигается посредством обеспечения программного обеспечения системы РЭО, спроектированного таким образом, чтобы ядра 4 многоядерного процессора 3 получали доступ к памяти 6 по общей шине 8 посредством распределения пропускной способности шины в соответствии с установленными значениями распределения (разделения) пропускной способности шины.

Пропускная способность шины может распределяться (разделяться) между ядрами 4 многоядерного процессора 3 на основании различных критериев. В предпочтительном варианте осуществления изобретения пропускная способность шины может быть надлежащим образом в равной степени распределена (разделена) между ядрами 4 многоядерного процессора 3, что приводит к равномерному распределению выделенной пропускной способности шины между ядрами 4. В другом варианте осуществления изобретения пропускная способность шины может быть надлежащим образом распределена (разделена) между ядрами 4 многоядерного процессора 3 на основании их фактического использования пропускной способности шины

Для обеспечения того, чтобы присвоенные распределения пропускной способности шины соответствовали ядрам 4, программное обеспечение системы РЭО предназначена для выполнения следующего:

фактическое применение или использование пропускной способности шины ядрами 4 многоядерного процессора 3 планируются с периодической проверкой относительно присвоенных распределений (разделений) пропускной способности для определения тех ядер 4, которые в конечном счете выходят за рамки присвоенных распределений (разделений) пропускной способности шины, и

ядра 4, которые определяются как выходящие за рамки присвоенных распределений пропускной способности шины, планируются как бездействующие (простаивающие) для компенсации данных выходов за пределы.

Использование пропускной способности шины ядрами 4 многоядерного процессора 3 обычно определяется посредством обращения к специальным аппаратным регистрам, известным как счетчики производительности 10, встроенные в ядра 4 и программируемые для подсчета и сохранения количества выполненных операций или событий, имеющих отношение к работе соответствующих ядер 4.

Для осуществления данного признака на практике система РЭО предназначена для приведения в действие следующего при выполнении:

счетчики производительности 10 должны выполнять подсчет и сохранение количества получения доступов ядер 4 многоядерного процессора 3 к памяти 6 по общей шине 8, что приводит к тому, что подсчеты, сохраненные в счетчиках производительности 10, являются индикативными при прочих равных условиях, в частности, в отношении рабочей частоты многоядерного процессора 3 и объема данных, передаваемых по общей шине 8, при фактическом использовании пропускной способности шины соответствующими ядрами 4 многоядерного процессора 3,

счетчики производительности 10 необходимо проектировать с периодическим считыванием, а подсчеты, считываемые со счетчиков производительности 10, необходимо проектировать с периодической проверкой относительно присвоенных индикативных значений распределений пропускной способности шины, присвоенных ядрам 4 многоядерного процессора 3 для определения тех ядер 4, которые, в конечном счете, выходят за пределы присвоенных распределений пропускной способности шины, и

ядра 4 многоядерного процессора 3, которые были определены как выходящие за пределы присвоенных распределений пропускной способности шины, необходимо перевести в режим простаивания (холостого хода) в течение одного или более периодов времени между следующими запланированными проверками для компенсации выхода за установленные границы.

С учетом того факта, что ядро 4 многоядерного процессора 3 обычно оборудовано множеством программируемых счетчиков производительности 10, обычно в количестве четырех или шести штук, и возможности счетчиков производительности 10 могут варьироваться в зависимости от архитектуры центрального процессорного устройства 2, программное обеспечение системы РЭО может быть спроектировано с обеспечением большого количества предоставлений доступа ядра 4 к памяти 6 по общей шине, которые подсчитываются посредством отдельного счетчика производительности 10, если ядра 4 многоядерного процессора 3 оборудованы счетчиками производительности 10, способными осуществлять подсчет количества предоставлений доступа ядра 4 к памяти 6 по общей шине 8, или посредством обращения к двум или более счетчикам производительности 10, если ядра 4 многоядерного процессора 3 оборудованы счетчиками производительности 10, которые не способны выполнять прямой подсчет количества предоставлений доступа ядра 4 к памяти 6 по общей шине 8.

Таким образом, в последнем случае программное обеспечение системы РЭО может быть спроектировано для осуществления того, чтобы первый счетчик производительности 10 выполнял подсчет количества операций считывания и записи строки кэша данных, а второй счетчик производительности 10 осуществлял подсчет количества операций считывания строки кэша команд, а третий счетчик производительности 10 и четвертый счетчик производительности 10 выполняли подсчет количества операций повторного заполнения кэша TLB (буфера динамической трансляции).

Программное обеспечение системы РЭО может также проектироваться таким образом, чтобы число предоставлений доступа ядра 4 к памяти 6 по общей шине 8 рассчитывалось как сумма подсчитанного количества операций считывания и регистрации строки кэша памяти, операций считывания строки кэша команд и операций повторного заполнения кэша TLB (буфера динамической трансляции).

В частности, количество предоставлений доступа ядра 4 к памяти 6 по общей шине 8 может быть рассчитано следующим образом:

```

L1D_CACHE_WB (обратная запись кэша данных) + L1I_CACHE_REFILL (повторное заполнение кэша команд) + k \cdot L1_TLB_REFILL (повторное заполнение кэша TLB данных и команд)

```

где k - это соотношение между размером строки кэша данных и объемом ввода кэша TLB, а счетчик производительности L1D\_CACHE\_WB надлежащим образом выполняет подсчет количества операций записи строки и считывания кэша данных посредством программирования регистра управления ядром путем "запрета механизма оптимизации, который предотвращает загрязнение кэша". Таким образом, все обращения к памяти принудительно направляются через кэш.

Более того, для обеспечения того, что подсчеты, сохраненные в счетчиках производительности 10 и представляющие собой количество предоставлений доступа ядер 4 многоядерного процессора 3 к памяти 6 по общей шине 8, являются достоверными и надежными применениями пропускной способности шины в наихудших условиях во время реального использования многоядерного процессора 3, программное обеспечение системы РЭО проектируется таким образом, что при выполнении доступ к периферийным устройствам 9 со стороны ядер 4 многоядерного процессора 3 надлежащим образом управлялся только

одним из ядер 4, что приводит к тому, что он выступает в качестве основного ядра 4 для доступа к периферийным устройствам 9, т.е. с обеспечением прямого доступа к ним только со стороны основного ядра 4 и косвенного доступа со стороны других ядер 4, которые таким образом выступают в качестве вторичных ядер 4 относительно основного ядра при получении доступа к периферийным устройствам 9.

Для применения данного отличительного признака на практике программное обеспечение системы РЭО проектируется таким образом, чтобы при выполнении периферийные устройства 9 подлежали виртуализации, что приводит к тому, что приложения, критические с точки зрения безопасности, выполняются различными ядрами 4, получающими непрямой доступ к периферийным устройствам 9 через подсоединенные логические порты, используя программные интерфейсы приложений (Application Programming Interfaces (APIs)). Соединение (ассоциация) между идентификаторами порта (Port ID) и периферийными устройствами 9 выполняется во время компиляции/трансляции.

Обеспечение управления периферийными устройствами 9 одним ядром 4 предотвращает конфликтные ситуация с периферией (периферийными устройствами) и появление ложных данных по причине конкурирующих/конфликтующих/одновременных доступов к периферийным устройствам 9 со стороны различных ядер 4, а также неожиданный доступ к периферийным устройствам 9 со стороны приложений, критичных с точки зрения безопасности, которые по замыслу (по проекту) не должны иметь доступа к периферийным устройствам 9, что приводит к тому, что конфликт между ядрами 4 ограничивается только доступом к общей шине 8 для получения доступа к памяти 6.

Основное ядро 4 может обеспечивать управление доступом к периферийным устройствам 9 либо исключительно, либо в дополнение к прочим установленным задачам. Если основное ядро 4 обеспечивает только исключительно управление доступом к периферийным устройствам 9, а счетчики производительности 10, подсоединенные к основному ядру 4, могут или фактически обеспечивают подсчет только количества предоставлений доступа к памяти 6, программное обеспечение системы РЭО может проектироваться для обеспечения доступа основного ядра 4 к периферийным устройствам 9 для считывания данных с них или записи данных на них с последующим или предварительным соответственно надлежащим доступом основного ядра 4 к памяти 6 для записи в память 6 данных, считанных с периферийных устройств 9 или считывания из памяти 6 данных, подлежащих записи на периферийные устройства 9. Данная связь между доступами к периферийным устройствам и памяти приводит к тому, что пропускная способность шины, которая требуется для доступа к периферийным устройствам 9, становится вычисляемой на основе пропускной способности шины, необходимой для доступа к памяти 6.

В частности, с учетом того факта, что время, необходимое основному ядру 4 для получения доступа к периферийным устройствам 9, может быть длиннее (и обычно длиннее) времени, необходимого для получения доступа к памяти 6, что приводит к ненадлежащему использованию распределения пропускной способности шины, выделенного основному ядру 4, доступ основного ядра 4 к периферийным устройствам 9 может быть выделен с весовой функцией, который выше, и в частности, в два раза или более раз выше весовой функции, выделенной для доступа основного ядра 4 к памяти 6, что приводит к тому, что пропускная способность шины, которая требуется для основного ядра 4 для доступа к периферийным устройствам 9, рассчитывается на основании пропускной способности шины, которая требуется для доступа к памяти 6, а весовые функции присваиваются для доступа основного ядра 4 к периферийным устройствам 9 и памяти 6.

Например, для учета фактического применения пропускной способности шины со стороны периферийных устройств 9, таких как последовательная линия, у которых может не быть автономного доступа к памяти 6 по общей шине 8, значение, выделенное основному ядру 4 и которое является индикативным распределением пропускной способности шины, выделенной основному ядру 4, проверяются относительно значения, которое формируется посредством умножения показания подечетов счетчика производительности 10, связанного с основным ядром 4, на коэффициент умножения, что приводит к тому, что фактическое применение пропускной способности шины данными периферийными устройствами 9 "корректируется" основным ядром 4, в то время как коэффициент умножения равен соотношению между временем, которое требуется для получения доступа к периферийным устройства 9, и временем, которое требуется для получения доступа к памяти 6 с увеличением на единицу.

Более того, весовая функция, назначенная (присвоенная/выделенная - здесь и далее термины идентичны) для доступа к периферийным устройствам 9 может оказаться зависимой от типа периферийных устройств 9, к которым необходимо получить доступ.

Например, для учета фактического применения пропускной способности шины периферийными устройствами 9, такими как линия Ethernet, которые программируются с автономным доступом к памяти 6 по общей шине 8, а именно без необходимости участия основного ядра 4, и невозможностью обеспечения этого соответствующими счетчиками производительности 10, запрограммированных на подсчет предоставлений доступа к памяти 6, значение, выделенное для основного ядра 4, и которое является индикативным распределением пропускной способности шины, выделенным основному ядру 4, проверяется относительно значения, получаемого посредством умножения двух показаний подсчетов счетчика производительности 10, связанного с основным ядром 4, что приводит к получению фактического применения (использования) пропускной способности шины периферийным устройством Ethernet 9, которое

"вычитается" (корректируется, дебитуется) у основного ядра 4.

Принимая во внимание тот факт, что пропускная способность общей шины 8 зависит от многоядерного процессора 3 и используемой памяти 6, а также от рабочей частоты, при которой будет работать многоядерный процессор 3 во время использования, применение пропускной способности шины при наихудших условиях ядрами 4 многоядерного процессора 3 может быть определено априори посредством реализации способа категоризации пропускной способности шины, который включает в себя

инициацию работы (настройку) многоядерного процессора 3 на (при) фиксированной рабочей частоте, при которой он будет эксплуатироваться (работать) во время использования,

выделение только одного из ядер 4 многоядерного процессора 3 для повторного доступа к памяти 6 по общей шине 8 для передачи строк кэша фиксированного размера в то время, когда доступ прочих ядер 4 к общей шине 8 предотвращается посредством переключения их в работу в непрекращающемся замкнутом цикле без доступа к памяти 6 по общей шине 8,

определение количества доступов рабочего ядра 4 к памяти 6 по общей шине 8 в течение установленного периода времени и

определение использования пропускной способности шины при наихудших условиях ядрами 4 многоядерного процессора 3 на основании количества доступов рабочего ядра 4 к памяти 6 по общей шине 8 в течение заданного периода времени и размера строк кэша.

Количество обращений рабочего ядра 4 к памяти 6 по общей шине 8 в течение заданного периода времени может быть надлежащим образом определено посредством обращения счетчика производительности 10 рабочего ядра 4 и, в частности, посредством инициации его для подсчета количества обращений (допусков) рабочего ядра 4 к памяти 6 по общей шине 8 в течение установленного периода времени, который соответствующим образом выбирается для предотвращения переполнения счетчика производительности 10, а затем считывания показаний подсчетов, сохраненных в счетчике производительности 10 рабочего ядра 4.

Рабочее ядро 4, которое получает доступ к памяти 6 по общей шине 8 так, что адрес памяти при каждом доступе отличается от предыдущего на величину, превышающую размер строк кэша для предотвращения считывания данных без обращения к общей шине 8.

Более того, память 6 разделена между ядрами 4 таким образом, что ядра 4 имеют различные сегменты памяти для предотвращения нежелательных ситуаций перекрытия обращений.

В качестве не ограничивающего примера возьмем период времени 100 мкс, рабочую частоту, при которой функционирует многоядерный процессор 3 во время применения, в 800 МГц, а размер строк кэша составляет 32 байт, тогда количество обращений рабочего ядра 4 к памяти 6 по общей шине 8 в 100 мкс составит 1.500, а итоговое использование пропускной способности шины при наихудших условиях составит 480 Мбайт/с.

На фиг. 2-4 показано практическое применение вышеуказанных функций в типовой среде РЭО, в которой работа системы РЭО основывается на так называемых основных и второстепенных функциях, где основная функция - это цикл, в течение которого выполняются второстепенные функции, например 32 или 64 второстепенные функции, а второстепенная функция - это период времени, в течение которого выполняются предварительно установленные операции, и в целом в течение порядка величин в несколько или десятых долей миллисекунд, например 20 мс. Следует принимать во внимание, что вспомогательные функции в основной функции используют одинаковые малые временные промежутки и синхронизируются по всем ядрам 4.

На фиг. 3 для сравнения показано, в качестве альтернативы, взаимосвязь между временем вспомогательной функции и периодами времени, именуемыми как периоды времени детализации пропускной способности шины, после которых фактическое использование пропускной способности шины ядрами 4 многоядерного процессора 3 периодически проверяется относительно выделенных распределений пропускной способности шины для определения тех ядер 4, которые в конечном счете выходят за пределы выделенных распределений пропускной способности шины.

Следует принимать во внимание, что периодические проверки синхронизированы среди ядер 4, что приводит к одновременной проверке фактического использования пропускной способности шины ядрами 4 многоядерного процессора 3.

Для выполнения значительного объема периодических проверок в течение времени вспомогательной функции период времени детализации пропускной способности шины должен выбираться значительно ниже по сравнению со временем вспомогательной функции, предпочтительней в виде функции количества ядер 4 многоядерного процессора 3, например как минимум в десять раз меньше количества ядер 4.

В завершении, на фиг. 4 показана периодическая проверка, выполняемая в отношении одного из ядер 4. По истечении периода времени детализации пропускной способности шины фактическое использование пропускной способности шины ядром 4 в течение периода времени детализации пропускной способности шины определяется на основании подсчетов, сохраненных в подсоединенном счетчике производительности 10, а затем проверяется относительно выделенного распределения пропускной способности шины. Если фактическое использование пропускной способности шины будет ниже выделенного

распределения пропускной способности шины, ядру 4 разрешается работать нормально в течение следующего периода времени детализации пропускной способности шины. Если вместо этого фактическое использование пропускной способности шины будет выше выделенного распределения пропускной способности шины, ядро 4 выключается из работы в течение одного или нескольких периодов детализации пропускной способности шины для компенсации переработки, в то время как количество периодов времени детализации пропускной способности шины, в течение которых ядро 4 выведено из работы, зависит от степени переработки, в частности оно зависит от соотношения переработки к выделенному распределению пропускной способности шины.

Подразумевается, что для определения фактического использования пропускной способности шины ядром 4 в течение периода времени детализации пропускной способности шины счетчик производительности 10, связанный с ядром 4, необходимо сбрасывать после каждой проверки для обнуления подсчетов, сохраненных в счетчике производительности 10. Это приводит к потере пропускной способности шины, которая не используется во время периода времени детализации пропускной способности шины и, таким образом, не может использоваться в течение следующего периода детализации пропускной способности шины.

По сравнению с решением, предоставленным в патенте США 8943287, данное изобретение предусматривает проверки фактического использования пропускной способности шины ядрами 4 многоядерного процессора 3, которые запланированы, с одной стороны, к проведению периодически с частотой, равной обратной функции периода времени детализации пропускной способности шины, а с другой стороны, синхронизированы между ядрами 4, что приводит к одновременной проверке фактического использования пропускной способности шины ядрами 4 многоядерного процессора 3 на всех ядрах 4 многоядерного процессора 3.

Синхронность проверок фактического использования пропускной способности шины ядрами 4 многоядерного процессора 3 приводит к успешному расчету WCET (наихудшего времени исполнения) по следующей форме:

$$WCET = WCET_0 + \sum_{i=1}^{N_{TstepNoLimit}} N_{realAcc_i} \cdot (N_{core} - 1) \cdot \left( \frac{T_{step}}{N_{Beq}} \right)$$

где:

$WCET_0$  - WCET (наихудшее время исполнения) испытуемого приложения, выполняемого на одном рабочем ядре,

T<sub>step</sub> - период детализации пропускной способности,

$N_{TstepNoLimit}$  - количество периодов времени детализации пропускной способности, имеющих отношение к измерению WCET $_0$  и в течение которых рабочее ядро не выходит за пределы выделенного распределения пропускной способности шины,

Beq - количество обращений рабочего ядра 4 к памяти 6 по общей шине 8 в течение установленного периода времени при использовании вышеуказанного способа категоризации пропускной способности шины.

N<sub>core</sub> - количество ядер 4 в многоядерном процессоре 3,

$N_{\text{realAcci}}$  - подсчеты, сохраненные в счетчике производительности рабочего ядра 4 і-го периода детализации пропускной способности.

#### ФОРМУЛА ИЗОБРЕТЕНИЯ

1. Система бортового радиоэлектронного оборудования (РЭО) (1), состоящая из центрального процессорного устройства (2) для реализации одного или нескольких приложений жесткого реального времени, критических с точки зрения безопасности, центральное процессорное устройство (2) включает в себя многоядерный процессор (3) с множеством ядер (4), память (6), общую шину (8), по которой многоядерный процессор (3) может получить доступ к памяти (6), и программное обеспечение РЭО, выполняемое многоядерным процессором (3), причем программное обеспечение РЭО предписывает во время выполнения ядрам (4) многоядерного процессора (3) обращаться за доступом к памяти (6) по общей шине (8) посредством распределения пропускной способности шины в соответствии с выделенным распределением пропускной способности шины;

отличающаяся тем, что многоядерный процессор (3) обеспечивает

планирование периодических проверок фактического использования пропускной способности шины ядрами (4) многоядерного процессора (3) в отношении выделенных распределений пропускной способности шины для определения тех ядер (4) в многоядерном процессоре (3), которые в конечном счете выходят за пределы выделенного распределения пропускной способности шины, а также планирование перевода в режим ожидания ядер (4), которые были определены как вышедшие за пределы выделенных распределений пропускной способности шины для компенсации переработки;

планирование проверок фактического использования пропускной способности шины ядрами (4) в многоядерном процессоре (3) относительно выделенных распределений пропускной способности шины

синхронно по всем ядрам (4) для получения фактического использования пропускной способности шины ядер (4) в многоядерном процессоре (3) при одновременной проверке.

- 2. Система РЭО (1) по п.1, в которой осуществляется перевод в режим ожидания ядер (4) в многоядерном процессоре (3), которые были определены как вышедшие за пределы выделенных распределений пропускной способности шины в течение одного или более временных интервалов между следующими запланированными проверками для компенсации переработки.

- 3. Система РЭО (1) по любому из указанных выше пунктов формулы, в которой ядра (4) многоядерного процессора (3) оборудованы подсоединенными счетчиками производительности (10) для подсчета операций, выполняемых соответствующими ядрами (4);

причем многоядерный процессор (3) выполнен с возможностью

предписания счетчикам производительности (10) выполнять подсчет количества обращений ядер (4) в многоядерном процессоре (3) к памяти (6) по общей шине (8) для обеспечения подсчета счетчиком производительности (10), которые отражают фактическое использование пропускной способности шины соответствующими ядрами (4) в многоядерном процессоре (3);

предписания и планирования счетчикам производительности (10) периодического выполнения считывания, а также проверки показаний подсчетов счетчиков производительности (10) относительно соответствующих выделенных индикативных значений распределений пропускной способности шины, выделенных ядрам (4) в многоядерном процессоре (3), для определения ядер (4), которые в конечном счете вышли на пределы выделенных распределений пропускной способности шины.

4. Система РЭО (1) по п.3, в которой выполняется предписание первому счетчику производительности (10) выполнять подсчет количества операций записи и считывания строк кэша, второму счетчику производительности (10) выполнять подсчет количества операций считывания строки кэша команд, а третьему счетчику производительности (10) и четвертому счетчику производительности (10) выполнять подсчет количества операций заполнения кэша TLB (буфера ассоциативной трансляции);

и предписание выполнения расчета количества обращений ядер (4) к памяти (6) по общей шине (8) в виде суммы подсчитанного количества операций записи и считывания строк кэша данных, операций считывания строк кэша команд и операций заполнения кэша TLB (буфера ассоциативной трансляции).

- 5. Система РЭО (1) по любому из указанных выше пунктов формулы, в которой пропускная способность шины равномерно распределяется среди ядер (4) в многоядерном процессоре (3).

- 6. Система РЭО (1) по любому из указанных выше пунктов формулы, в которой многоядерный процессор (3) обеспечивает доступ к периферийным устройствам (9) по общей шине (8) и предписание только одному основному ядру (4) многоядерного процессора (3) управлять доступом к периферийным устройствам (9) из всех ядер (4) в многоядерном процессоре (3), что приводит к тому, что прямой доступ к периферийным устройствам (9) предоставляется только основным ядром (4) при наличии непрямого доступа со стороны вторичных ядер (4) через основное ядро.

- 7. Система РЭО (1) по п.6, в которой многоядерный процессор (3) дополнительно обеспечивает предписание обращения основного ядра (4) к периферийным устройствам (9) для считывания с них данных или записи на них данных, предшествовало или следовало за ним соответствующее обращение основного ядра (4) к памяти (6) для записи в память (6) данных, считанных с периферийных устройств (9), или считывания из памяти (6) данных, записанных на периферийных устройствах (9), создавая таким образом связь между обращениями к периферийным устройствам и памяти, что приводит к расчету пропускной способности шины, которая требуется для обращения к периферийным устройствам (9) на основании пропускной способности шины, необходимой для обращения к памяти (6).

- 8. Система РЭО (1) по п.7, в которой многоядерный процессор (3) дополнительно обеспечивает предписание обращения основного ядра (4) к периферийным устройствам (9), назначение весовой функции, которая выше, чем весовая функция, назначенная для обращения основного ядра (4) к памяти (6), что приводит к тому, что пропускная способность шины, необходимая для обращения к периферийным устройствам (9), рассчитывается на основании пропускной способности, необходимой для обращения к памяти (6), а весовые функции назначаются для обращения основного ядра (4) к периферийным устройствам (9) и памяти (6).

- 9. Система РЭО (1) по п.8, в которой весовая функция, назначенная для обращения основного ядра (4) к периферийным устройствам (9), зависит от типа периферийного устройства (9), к которому обеспечивается доступ.

- 10. Способ категоризации пропускной способности шины в системе РЭО (1) по любому из предшествующих пунктов формулы изобретения при фиксированной рабочей частоте, на которой используется многоядерный процессор (3), при этом способ включает

инициацию работы многоядерного процессора (3) с фиксированной рабочей частотой,

предписание только одному основному ядру из ядер (4) в многоядерном процессоре (3) циклически обращаться к памяти (6) по общей шине (8) для передачи строк кэша фиксированного размера,

определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени и

определение пропускной способности шины на основании количества обращений основного ядра

- (4) к памяти (6) по общей шине (8) в течение установленного периода времени и размера строк кэша.

- 11. Способ по п.10, в котором ядра (4) в многоядерном процессоре (3) оборудованы соответствующими счетчиками производительности (10) для подсчета операций, выполняемых соответствующими ядрами (4);

в котором определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени включает в себя

предписание одному или более счетчикам производительности (10) основного ядра (4) выполнить подсчет обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени,

считывание показаний по меньшей мере одного счетчика производительности (10) основного ядра (4), который участвует в подсчете количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени, и

определение количества обращений основного ядра (4) к памяти (6) по общей шине (8) в течение установленного периода времени на основании показаний, считанных со счетчиков производительности (10).

12. Способ по любому из пп. 10 или 11, дополнительно включающий

предписание прочим ядрам (4) в многоядерном процессоре (3) функционировать в бесконечном замкнутом цикле без доступа к памяти (6) по общей шине (8).

13. Способ определения распределений пропускной способности шины, подлежащих выделению ядрам (4) в многоядерном процессоре (3) в системе РЭО (1) по любому из предшествующих пп.1-9, способ включает в себя

определение характеристик пропускной способности шины по любому из пп.10-12 и распределение пропускной способности шины среди ядер (4) в многоядерном процессоре (3).

14. Способ по п.13, в котором распределение пропускной способности шины среди ядер (4) в многоядерном процессоре (3) состоит из

равного распределения пропускной способности шины среди ядер (4) в многоядерном процессоре (3).

15. Многоядерный процессор (3) для системы РЭО (1), обеспечивающий выполнение программного обеспечения, предписывающего системе РЭО (1) принимать конфигурацию по любому из пп.1-9.

Фиг. 1

Фиг. 3

Фиг. 4